iCE40HX8K-EVB

| Price | 29.95 EUR |

|---|

iCE40HX8K-EVB is low cost development board for iCE40 FPGA family from Lattice Semiconductor.

The interesting part about this family of FPGAs is that there is a completely free and open source development tool available.

Using this free tool you can compile Verilog designs and upload them to the FPGA. More inforomation on the link in Software section.

iCE40HX8K-EVB has 34 pin bus connector which allows the easy hardware expansion of the board with additional modules like: iCE40-ADC with 100Mhz ADC; iCE40-DAC with 100Mhz DAC; iCE40-IO with VGA, PS2 and IrDA transciever; MOD-DIO with logic analyzer level shifter with programmable 1.5-5.5V threshold. Up to 4 x ADC and 4 x DAC expansion modules can be connected on same bus (if you use iCE40-IO on the same bus then only up to 2 x ADC and 1 x DAC).

FEATURES

- iCE40HX8K-CT256 FPGA 7680 Logic cells, 960 LABs, 128 K embedded RAM bits

- 512KB SRAM organized as 256Kx16bit 10ns

- 2MB Serial Flash

- 2 user status LEDs

- Programming successful status LED

- 2 user buttons

- Reset button

- Power jack for 5V DC external power supply

- PGM connector (all signals at PGM1 @ 3.3V DC)

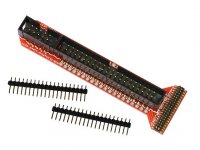

- 34 pin connector bus

- 4 x 40 pin connectors for GPIOs

- 100 Mhz oscillator

- Power supply DCDC regulators

- Power supply status LED

- Dimentions: 65x67mm ~ (2.56x2.64)"

DOCUMENTS

HARDWARE

SOFTWARE

- IceStorm FOSS tools for Linux

- WinIceProg tool for Windows

- Lattice official IceCube2 for Windows

- OLIMEXINO-32U4 programmer sketch

- Programming iCE40HX1K-EVB with Raspberry Pi

- Programming iCE40HX8K-EVB with SBC

- Blinking LED demo code

- VGA and PS2 demo code

- nextpnr portable FPGA routing tool

- Programming iCE40HX8K-EVB with FT2232H

COMMUNITY

FAQ

- I can't program this chip via JTAG. I am use the on-board row of pinholes named "JTAG". What is wrong?

- The iCE40HX8K chip has no JTAG interface. The header is left-over from initial releases of official documentation. Refer to the family datasheet to confirm it. The only way to program it is via SPI.

-

Newly purchased boards can't be programmed via Arduino IDE. What is the difference compared to previous revisions?

-

The SPI memory had to be changed due to unvailability of the original one. New memory is not supported by the old SPI flash library, use this library link. Also refer to the wiki article and latest schematic.